US 20100218196A1

### (19) United States

# (12) Patent Application Publication Leung et al.

# (54) SYSTEM, METHODS AND APPARATUS FOR PROGRAM OPTIMIZATION FOR MULTI-THREADED PROCESSOR ARCHITECTURES

(75) Inventors: Allen K. Leung, New York, NY

(US); Benoit Meister, New York, NY (US); Nicolas T. Vasilache, New York, NY (US); David E. Wohlford, Portland, OR (US); Cedric Bastoul,

Voisins-le-Bretonneux (FR); Peter Szilagyi, Medina, NY (US); Richard A. Lethin, New York, NY

(US)

Correspondence Address:

FOLEY & LARDNER LLP P.O. BOX 80278 SAN DIEGO, CA 92138-0278 (US)

(73) Assignee: Reservoir Labs, Inc.

(21) Appl. No.: 12/762,281

(22) Filed: Apr. 16, 2010

#### Related U.S. Application Data

(63) Continuation-in-part of application No. 12/365,780, filed on Feb. 4, 2009, Continuation-in-part of application No. 12/561,152, filed on Sep. 16, 2009. (10) **Pub. No.: US 2010/0218196 A1** (43) **Pub. Date:** Aug. 26, 2010

(60) Provisional application No. 61/170,261, filed on Apr. 17, 2009, provisional application No. 61/065,294, filed on Feb. 8, 2008, provisional application No. 61/097,799, filed on Sep. 17, 2008.

#### **Publication Classification**

(51) **Int. Cl.**

**G06F 9/44** (2006.01) **G06F 9/46** (2006.01)

(52) **U.S. Cl.** ...... 718/107; 717/160

#### (57) ABSTRACT

Methods, apparatus and computer software product for source code optimization are provided. In an exemplary embodiment, a first custom computing apparatus is used to optimize the execution of source code on a second computing apparatus. In this embodiment, the first custom computing apparatus contains a memory, a storage medium and at least one processor with at least one multi-stage execution unit. The second computing apparatus contains at least two multistage execution units that allow for parallel execution of tasks. The first custom computing apparatus optimizes the code for parallelism, locality of operations and contiguity of memory accesses on the second computing apparatus. This Abstract is provided for the sole purpose of complying with the Abstract requirement rules. This Abstract is submitted with the explicit understanding that it will not be used to interpret or to limit the scope or the meaning of the claims.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

|                      |                  |         |                                         |                            |                                         |                |                | 1090            |                |             | 1030                        |

|----------------------|------------------|---------|-----------------------------------------|----------------------------|-----------------------------------------|----------------|----------------|-----------------|----------------|-------------|-----------------------------|

|                      |                  |         |                                         |                            |                                         |                |                |                 |                |             |                             |

| Instruction<br>Fetch | )II              |         |                                         | T                          |                                         |                |                | T               |                |             |                             |

| Y WINT               |                  | Instruc |                                         |                            |                                         |                |                |                 |                |             |                             |

|                      |                  |         |                                         | Operat<br>Addres<br>Genera | is                                      |                |                |                 |                |             |                             |

|                      |                  |         | *************************************** |                            | *************************************** | Opera<br>Fetch | nd             |                 |                |             |                             |

|                      |                  |         |                                         |                            |                                         |                |                | Instru<br>Execu |                |             |                             |

| $T_{\theta}$         |                  | .1      |                                         | 1                          | $\overline{\zeta_2}$                    |                | Ť <sub>3</sub> | 1               | $T_4$          | Resu        | lts Store<br>T <sub>5</sub> |

|                      |                  |         |                                         |                            |                                         |                |                |                 |                |             |                             |

|                      | nstruct<br>Fetch | lion    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                            |                                         |                |                |                 |                |             |                             |

|                      | nstruct<br>Fetch | lion    | Instruc                                 |                            |                                         |                |                |                 |                |             |                             |

|                      |                  | ion     | Decod<br>Regist                         | le                         |                                         |                |                |                 |                |             |                             |

|                      |                  | tion    | Decod                                   | le                         | Exec                                    | ıte            |                |                 |                |             |                             |

|                      |                  | lion    | Decod<br>Regist                         | le                         | Exect                                   | ate            | Memo Acces     | uv<br>s         |                |             |                             |

|                      |                  | tion    | Decod<br>Regist                         | le                         | Exect                                   | ate            | Memo<br>Acces  | ary<br>s        | Regis<br>Write | ter<br>Back |                             |

|                      |                  | tion    | Decod<br>Regist                         | le                         |                                         |                | Memo<br>Acces  | nry<br>s        | Regis<br>Write | ter<br>Back |                             |

|                      |                  | tion    | Decod<br>Regist                         | le                         |                                         | ate            | Memo           | ory<br>s        | Regis<br>Write | ter<br>Back |                             |

FIG. 13

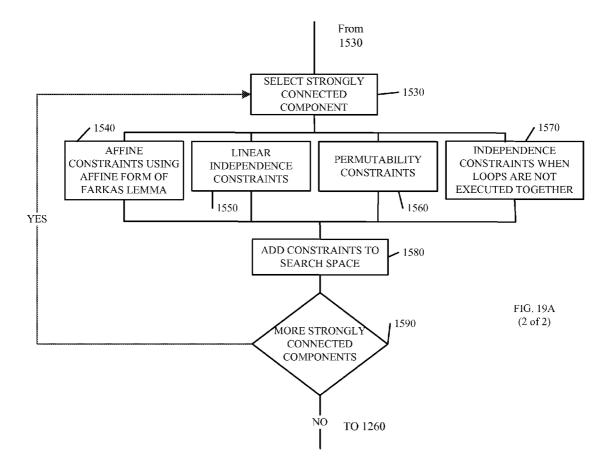

FIG. 19A (1 of 2)

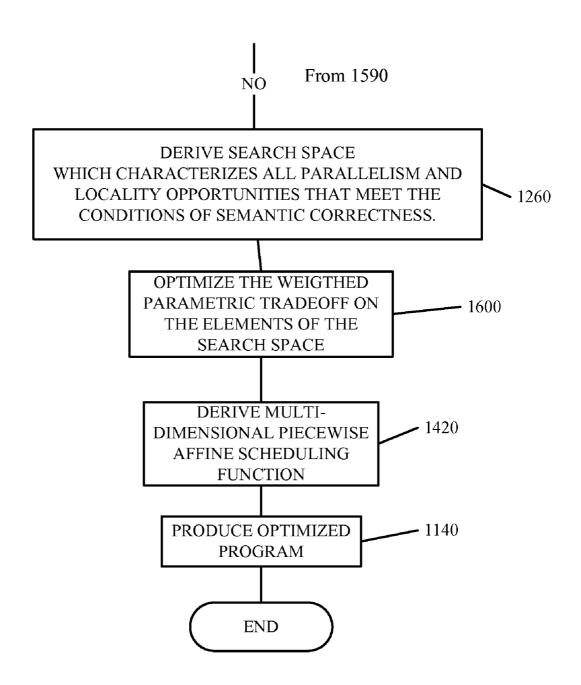

FIG. 19B

FIG. 21B (2 of 2)

FIG. 23

US 2010/0218196 A1

FIG. 25(b)

#### SYSTEM, METHODS AND APPARATUS FOR PROGRAM OPTIMIZATION FOR MULTI-THREADED PROCESSOR ARCHITECTURES

## CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation-in-part of U.S. application Ser. No. 12/365,780 entitled "METHODS AND APPARATUS FOR LOCAL MEMORY COMPACTION", filed Feb. 4, 2009, which claims priority to U.S. Provisional Application Ser. No. 61/065,294 filed, Feb. 8, 2008. Additionally, this application is a Continuation-in-part of U.S. application Ser. No. 12/561,152 entitled "METHODS AND APPARATUS FOR JOINT PARALLELISM AND LOCAL-ITY OPTIMIZATION IN SOURCE CODE COMPILA-TION" filed, Sep. 16, 2009, which claims priority to U.S. Provisional Application Ser. No. 61/097,799 filed, Sep. 17, 2008. Further, this application is related to and claims the benefit of priority to U.S. Provisional Application Ser. No. 61/170,261 entitled "AUTOMATIC CUDA MAPPING IN THE R-STREAM COMPILER", filed Apr. 17, 2009. Priority is claimed to each of the above applications which are incorporated by reference herein in their entirety.

#### GOVERNMENT INTEREST

[0002] Portions of this invention were made with U.S. Government support under contracts/instruments Department of Energy SBIR DE-FG02-08ER85149, Defense Advanced Research Projects Agency F03602-03-C-0033; Department Of Energy SBIR W9113M-08-C-0146. The U.S. Government has certain rights.

#### FIELD OF THE INVENTION

[0003] The present invention generally concerns computer programming. More particularly, the invention concerns a system, methods, and apparatus for source code compilation.

#### BACKGROUND OF THE INVENTION

[0004] The progression of the computer industry in recent years has illustrated the need for more complex processor architectures capable of processing large volumes of data and executing increasingly complex software. A number of systems resort to multiple processing cores on a single processor. Other systems include multiple processors in a single computing device. Additionally, many of these systems utilize multiple threads of execution per processing core. One limitation that these architectures experience is that the current commercially available compilers cannot efficiently take advantage of the increase of computational resources.

[0005] In the software design and implementation process, compilers are responsible for translating the abstract operational semantics of the source program into a form that makes efficient use of a highly complex heterogeneous machine. Multiple architectural phenomena occur and interact simultaneously; this requires the optimizer to combine multiple program transformations. For instance, there is often a tradeoff between exploiting parallelism and exploiting locality to reduce the ever widening disparity between memory bandwidth and the frequency of processors: the memory wall. Indeed, the speed and bandwidth of the memory subsystems

have always been a bottleneck, which worsens when going to multi-core. This memory wall is further exacerbated by noncontiguous memory accesses.

[0006] On many architectures, the order in which memory locations are read and written has a profound effect on how they are issued in hardware. Bad memory access patterns may result in multiple factors of loss of memory bandwidth. Since optimization problems are associated with huge and unstructured search spaces, the combinational task of optimizing a program balancing these hardware requirements is poorly achieved by current compilers, resulting in weak scalability and disappointing sustained performance.

[0007] Even when programming models are explicitly parallel (threads, data parallelism, vectors), they usually rely on advanced compiler technology to relieve the programmer from scheduling and mapping the application to computational cores, understanding the memory model and communication details. Even provided with enough static information or annotations (OpenMP directives, pointer aliasing, separate compilation assumptions), compilers have a hard time exploring the huge and unstructured search space associated with these mapping and optimization challenges. Indeed, the task of the compiler can hardly been called optimization anymore, in the traditional meaning of reducing the performance penalty entailed by the level of abstraction of a higher-level language. Together with the run-time system (whether implemented in software or hardware), the compiler is responsible for most of the combinatorial code generation decisions to map the simplified and ideal operational semantics of the source program to the highly complex and hetero-

[0008] Current trends in computer architecture amplify the utilization of multiple processor cores on a chip. Modern multiple-core computer architectures that include general purpose multi-core architectures and specialized parallel architectures such as the Cell Broadband Engine and Graphics Processing Units (GPUs) have very high computation power per chip. Current and future architectures are increasingly evolving towards heterogeneous mixes of general purpose and specialized parallel architectures. One architectural concept of particular interest is the massively multi-threaded execution model. In this model, a large number of virtual threads of execution are mapped to a multiplicity of physical execution units. These virtual threads can be quickly switched in and out of the execution unit by the hardware runtime. In particular, when a long latency memory access is requested, another thread is scheduled to hide the latency of the memory access. Such an execution model comes with the need for the application to exhibit enough parallelism. Increased parallelism may be obtained by explicitly writing programs with more parallelism or by using auto-paralleliz-

[0009] While programming such systems by hand has been demonstrated for a range of applications, this is a difficult and costly endeavor; likely one to be revisited to allow the application to port to rapidly arriving new generations and configurations of heterogeneous architectures and programming abstractions that change the optimization tradeoffs. Recent programming models and abstractions include but are not limited to Partitioned Global Address Space (PGAS), Compute Unified Device Architecture (CUDA) and Open Computing Language (OpenCL). The application developer is also confronted to a programmability wall in addition to the memory wall and is responsible for writing a correct parallel

application using one of these recent programming abstractions. Obtaining reasonable performance is an additional difficult task best left to a compiler.

[0010] The polyhedral model is a powerful framework to unify coarse grained and fine-grained parallelism extraction with locality and communication contiguity optimizations. To date, this promise has not yet been completely fulfilled as no existing affine scheduling, fusion and communication contiguity technique can perform all these optimizations in a unified (i.e., non-phase ordered) and unbiased manner. Typically, parallelism optimization algorithms optimize for degrees of parallelism, but cannot be used to optimize both locality and contiguity of communications. In like manner, algorithms used for locality optimization cannot be used both for extracting parallelism and optimizing the contiguity of communications. Additional difficulties arise when optimizing source code for the particular architecture of a target computing apparatus.

[0011] Therefore there exists a need for improved source code optimization methods and apparatus that can optimize parallelism, locality and contiguity of memory accesses at multiple level of the heterogeneous hardware hierarchy.

# SUMMARY OF THE INVENTION

[0012] The present invention provides a system, apparatus and methods for overcoming some of the difficulties presented above. Various embodiments of the present invention provide a method, apparatus, and computer software product for optimization of a computer program on a first computing apparatus for execution on a second computing apparatus.

[0013] In an exemplary provided method computer program source code is received into a memory on a first computing apparatus. In this embodiment, the first computing apparatus' processor contains at least one multi-stage execution unit. The source code contains at least one arbitrary loop nest. The provided method produces program code that is optimized for execution on a second computing apparatus. In this method the second computing apparatus contains at least two multi-stage execution units. With these units there is an opportunity for parallel operations. In its optimization of the code, the first computing apparatus takes into account the opportunity for parallel operations and locality and analyses the tradeoff of execution costs between parallel execution and serial execution on the second computing apparatus. In this embodiment, the first computing apparatus minimizes the total costs and produces code that is optimized for execution on the second computing apparatus.

[0014] In another embodiment, a custom computing apparatus is provided. In this embodiment, the custom computing apparatus contains a storage medium, such as a hard disk or solid state drive, a memory, such as a Random Access Memory (RAM), and at least one processor. In this embodiment, the at least one processor contains at least one multistage execution unit. In this embodiment, the storage medium is customized to contain a set of processor executable instructions that, when executed by the at least one processor, configure the custom computing apparatus to optimize source code for execution on a second computing apparatus. The second computing apparatus, in this embodiment, is configured with at least two multi-stage execution units. This configuration allows the execution of some tasks in parallel, across the at least two execution units and others in serial on a single execution unit. In the optimization process the at least one processor takes into account the tradeoff between the cost of parallel operations on the second computing apparatus and the cost of serial operations on a single multi-stage execution unit in the second computing apparatus.

[0015] In a still further embodiment of the present invention a computer software product is provided. The computer software product contains a computer readable medium, such as a CDROM or DVD medium. The computer readable medium contains a set of processor executable instructions, that when executed by a multi-stage processor within a first computing apparatus configure the first computing apparatus to optimize computer program source code for execution on a second computing apparatus. Like in the above described embodiments, the second computing apparatus contains at least two execution units. With at least two execution units there is an opportunity for parallel operations. The configuration of the first computing apparatus includes a configuration to receive computer source code in a memory on the first computing apparatus and to optimize the costs of parallel execution and serial execution of tasks within the program, when executed on the second computing apparatus. The configuration minimizes these execution costs and produces program code that is optimized for execution on the second computing apparatus.

# BRIEF DESCRIPTION OF THE DRAWINGS

[0016] Various embodiments of the present invention taught herein are illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings, in which:

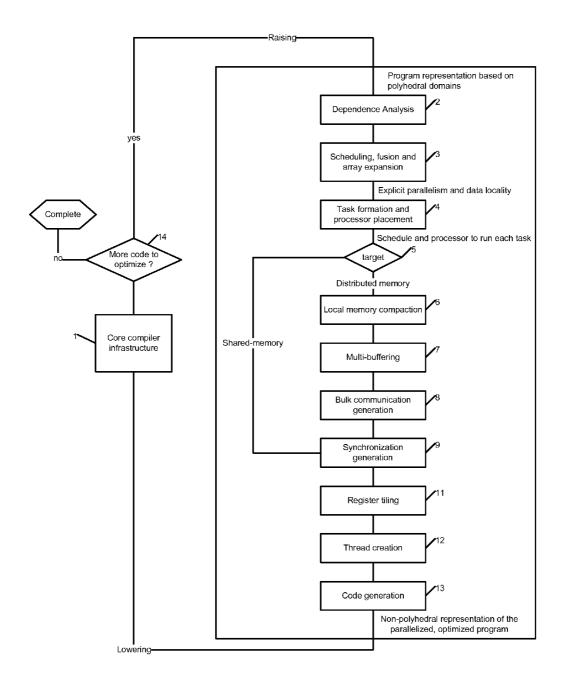

[0017] FIG. 1 is an overview of an exemplary compiler architecture consistent with provided embodiments;

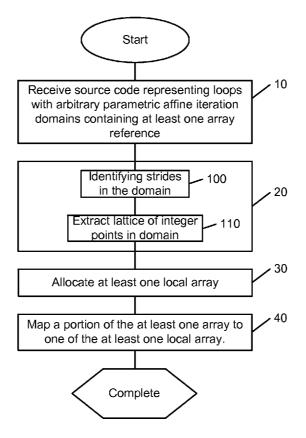

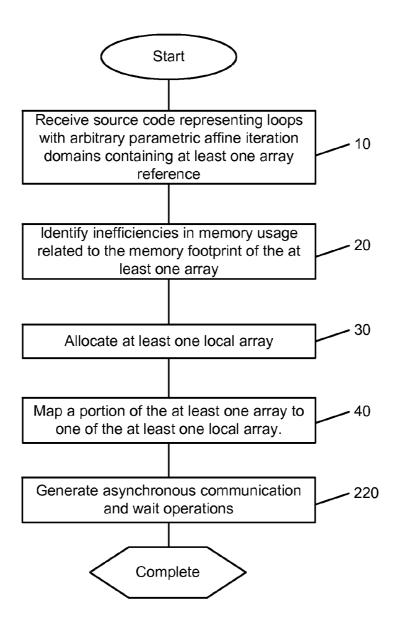

[0018] FIG. 2 illustrates the operational flow of one embodiment of a provided local memory compaction module:

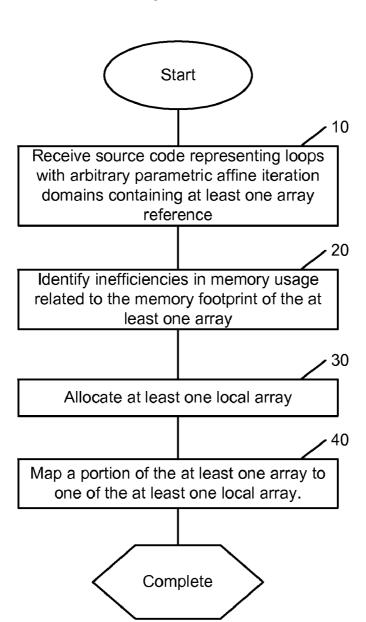

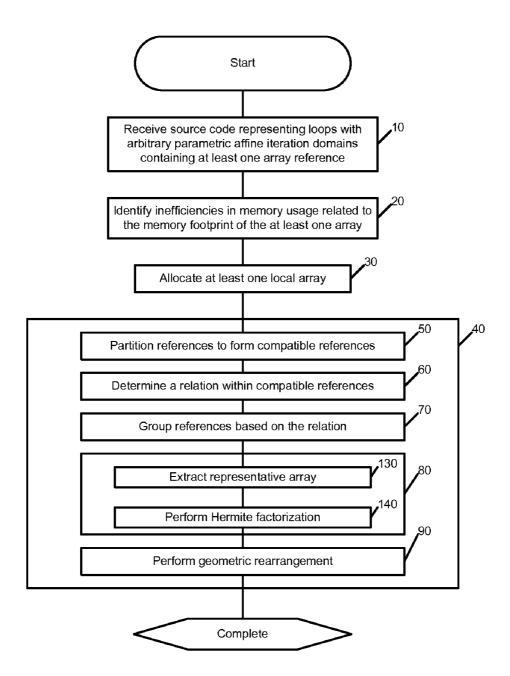

[0019] FIG. 3 illustrates the operational flow of another provided local memory compaction module, in which array references are partitioned into groups and algebraic and geometric data re-indexing functions are computed;

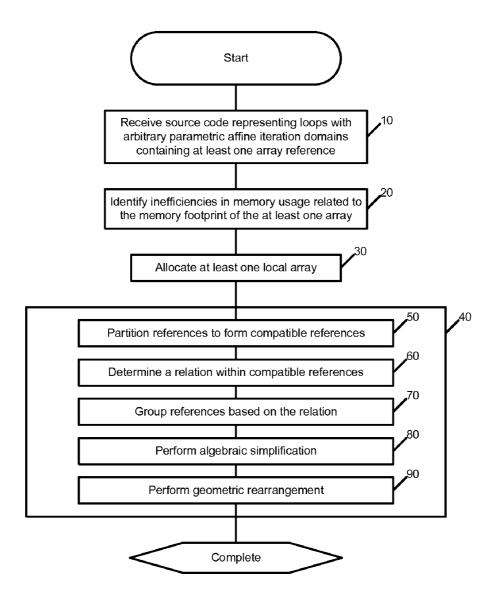

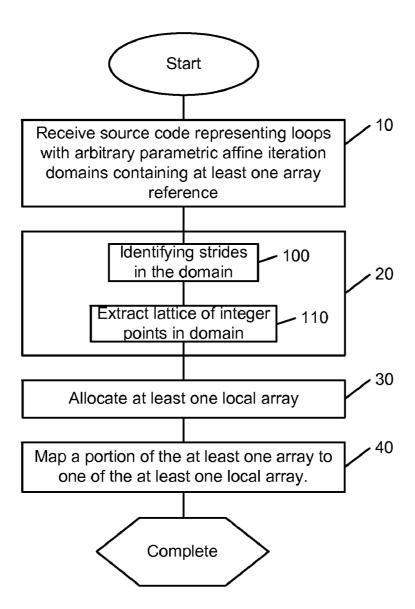

[0020] FIG. 4 illustrates the operational flow of an additional local memory compaction module in which inefficiencies in memory usage are determined using lattices of integer points;

[0021] FIG. 5 illustrates the operational flow of an additional local memory compaction module for reducing the inefficiencies in local memory usage by extracting representative array references and producing re-indexing functions using Hermite factorizations;

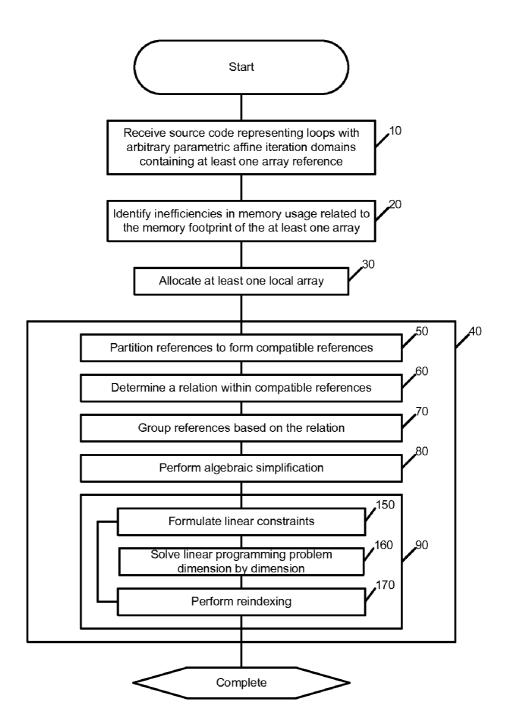

[0022] FIG. 6 illustrates the operational flow of an additional local memory compaction module for computing data re-indexing functions by producing linear constraints and solving a series of linear programming problems.

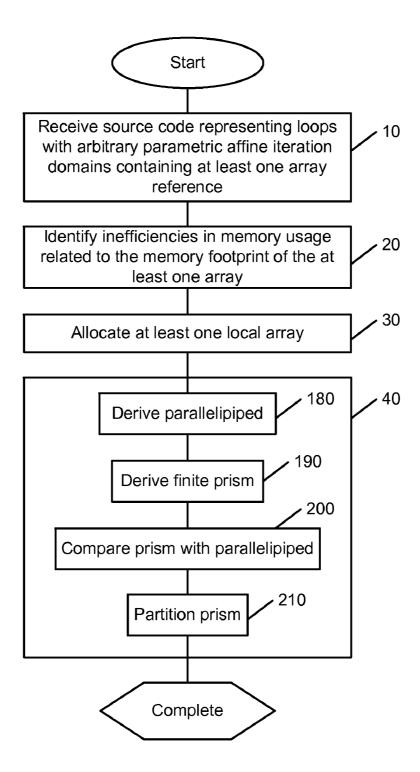

[0023] FIG. 7 illustrates the operational flow of an additional local memory compaction module for computing data re-indexing functions by finding a prism of triangular base that encloses the accessed data set and reducing the memory requirements of the enclosed data region by transforming the data elements that lie within a subset of the prism of triangular base.

[0024] FIG. 8 illustrates the operational flow of an additional local memory compaction module using data re-indexing information to produce abstract communication commands and schedule computations and communications for the program in such a way that their executions overlap;

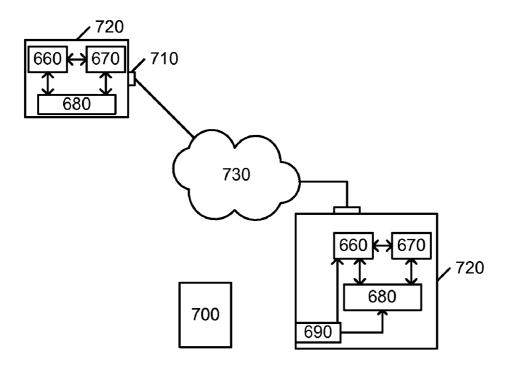

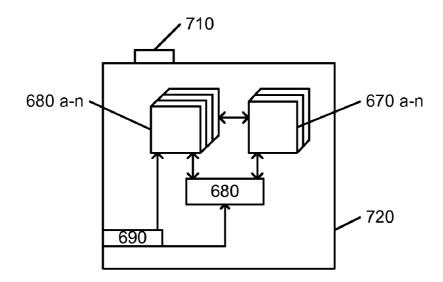

[0025] FIG. 9 illustrates a computing apparatus and computer software product consistent with provided embodiments:

[0026] FIG. 10 illustrates a computer network and a computing apparatus consistent with provided embodiments;

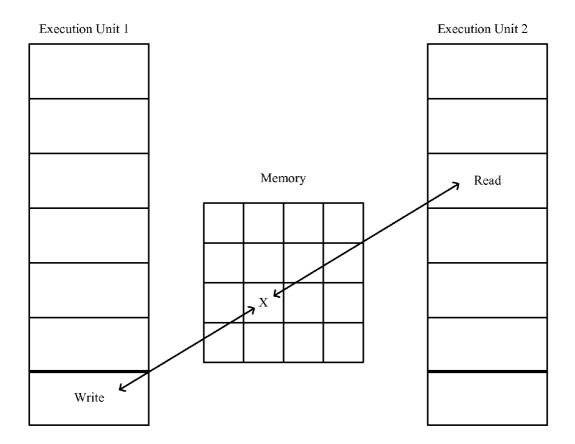

[0027] FIG. 11 illustrates processors with multi-stage execution units;

[0028] FIG. 12 illustrates a processor with multiple multistage execution units;

[0029] FIG. 13 illustrates an embodiment of a provided method

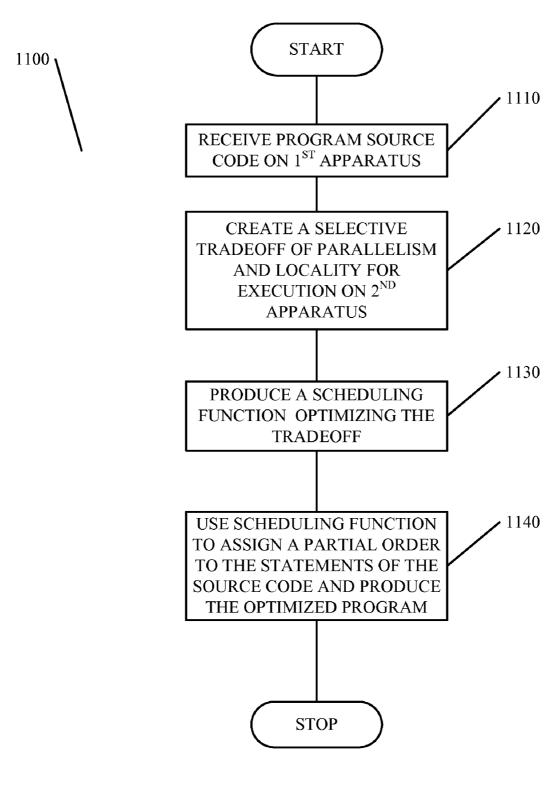

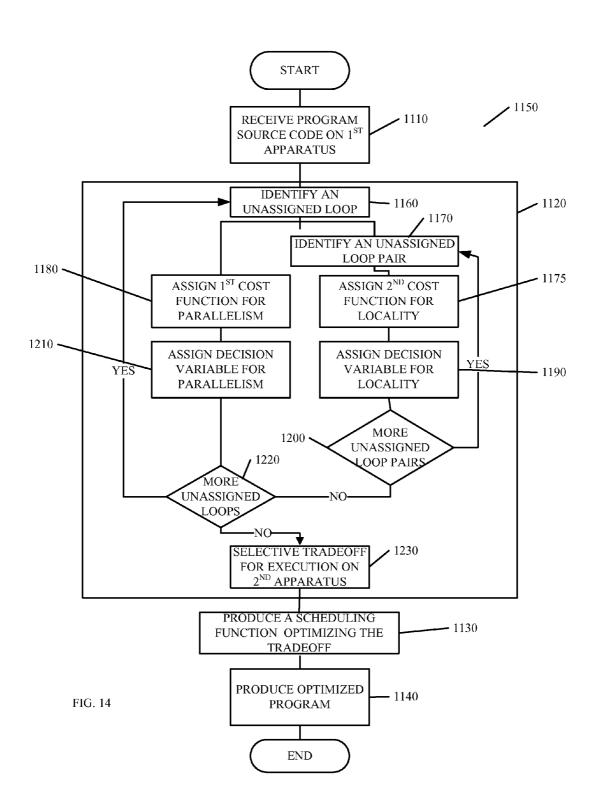

[0030] FIG. 14 illustrates an embodiment of a provided method;

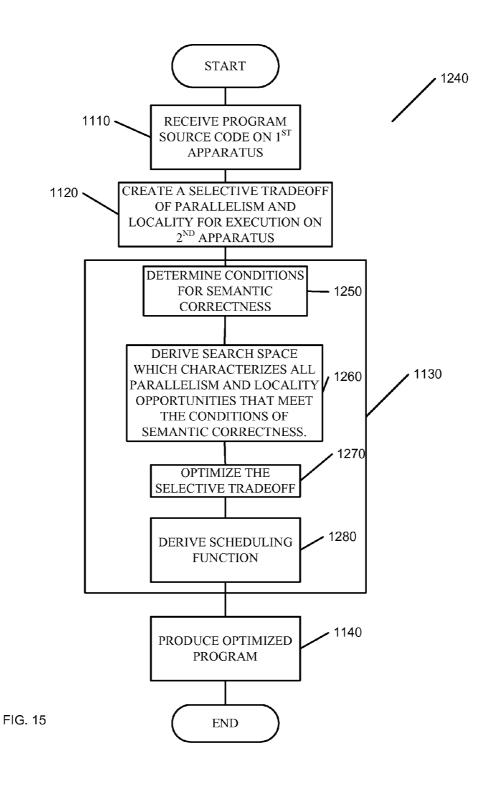

[0031] FIG. 15 illustrates an embodiment of a provided method;

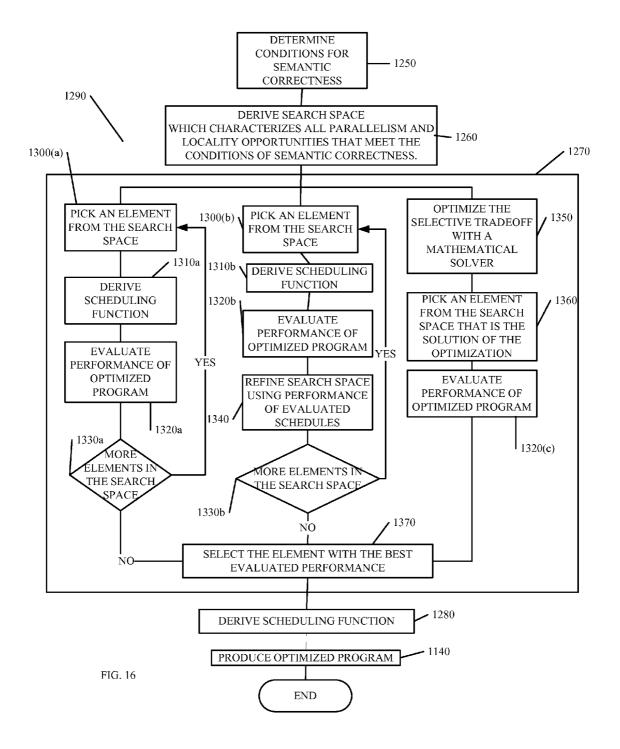

[0032] FIG. 16 illustrates an embodiment of a provided method;

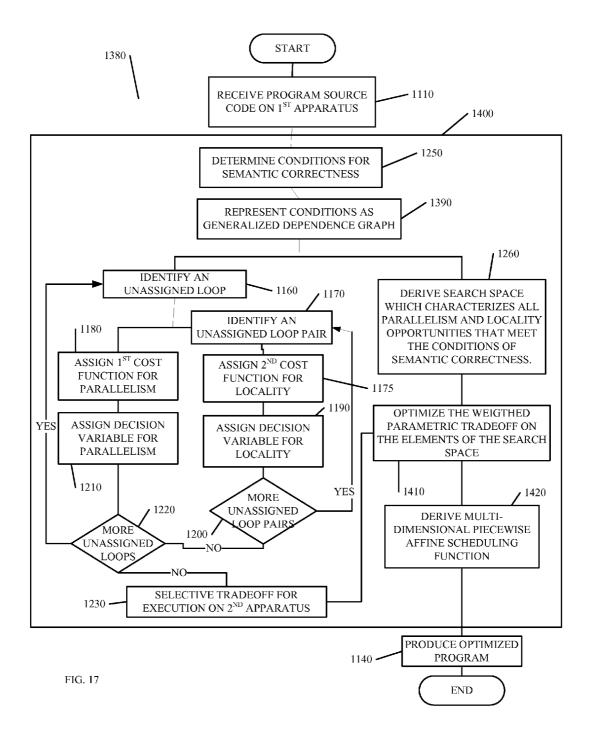

[0033] FIG. 17 illustrates an embodiment of a provided method:

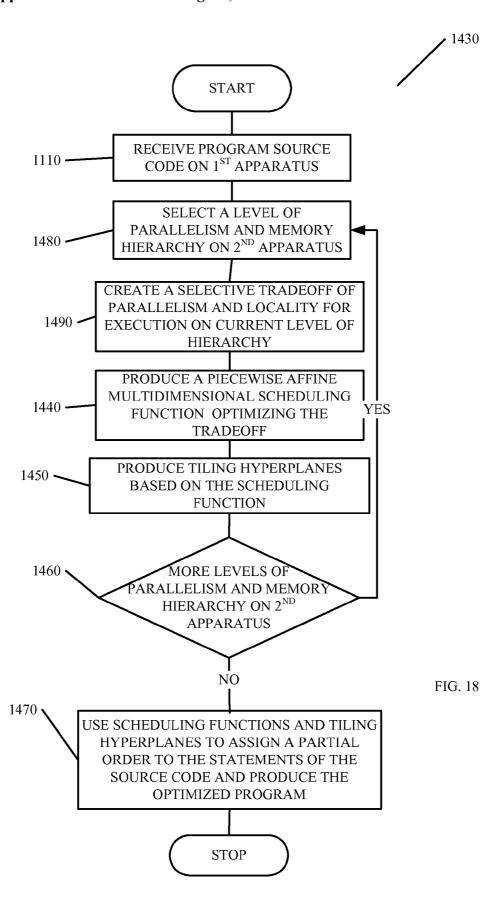

[0034] FIG. 18 illustrates an embodiment of a provided method;

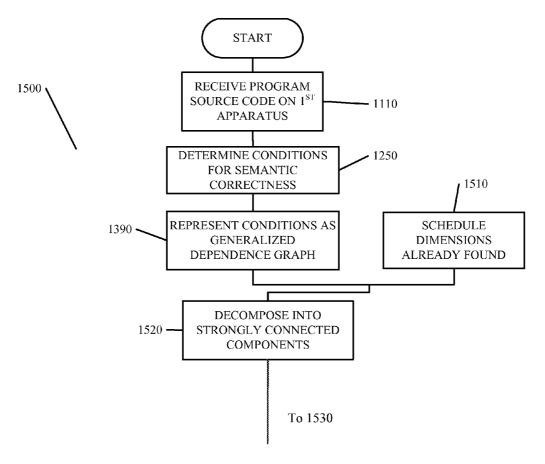

[0035] FIGS. 19(a) and 19(b) illustrate an embodiment of a provided method;

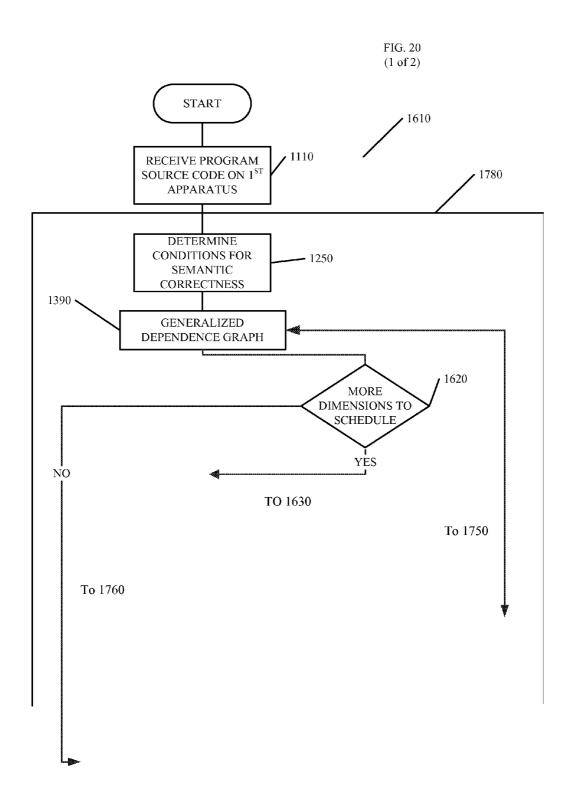

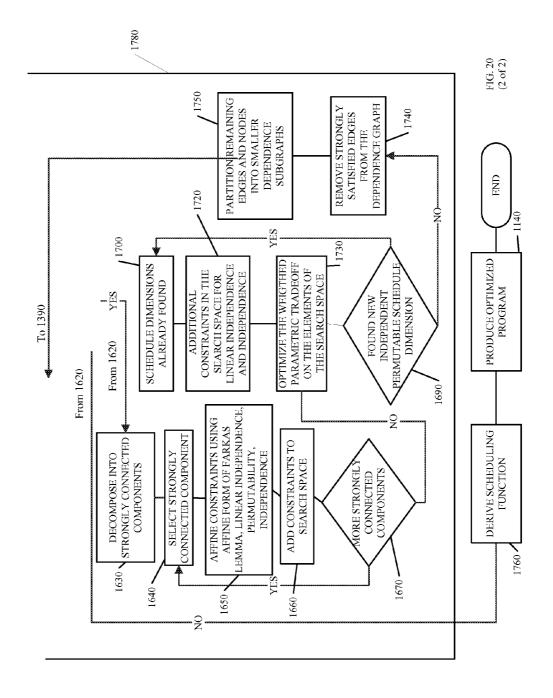

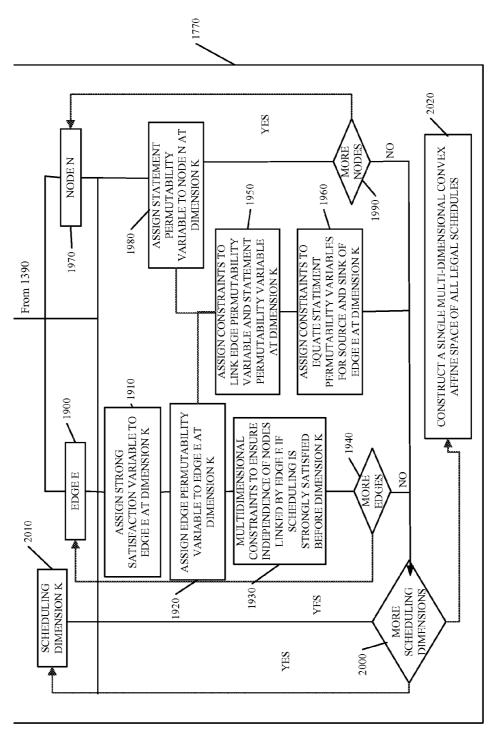

[0036] FIG. 20 illustrates an embodiment of a provided method:

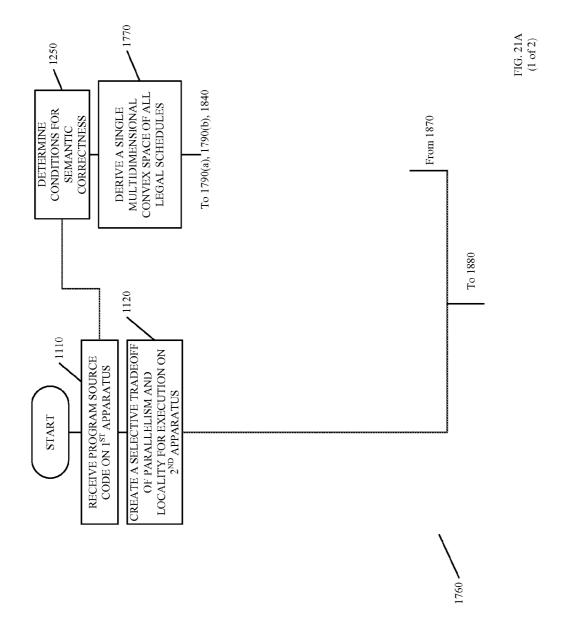

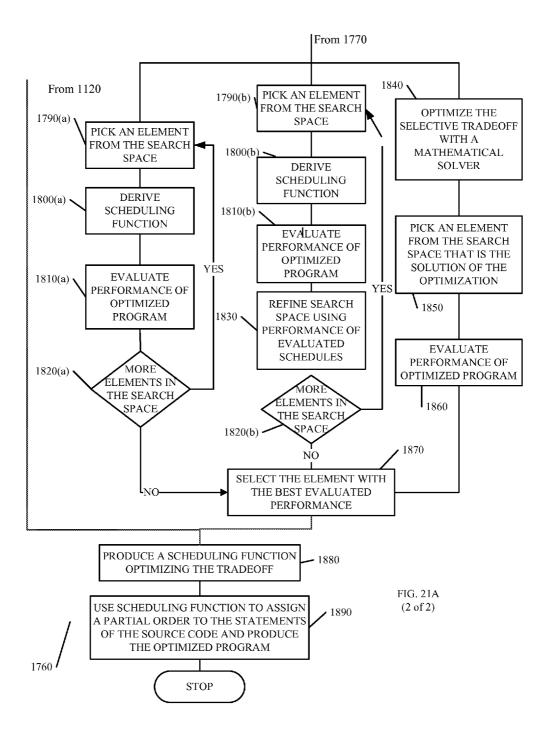

[0037] FIGS. 21(a) and 21(b) illustrate an embodiment of a provided method; and

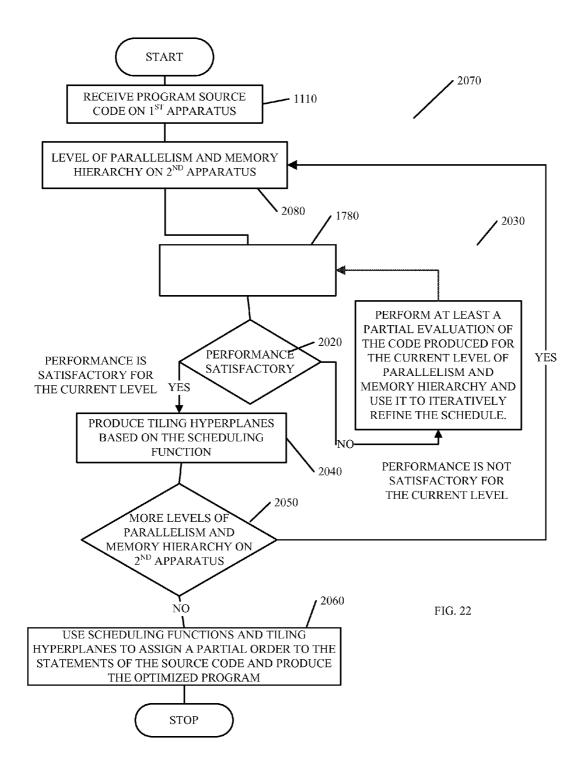

[0038] FIG. 22 illustrates an embodiment of a provided method:

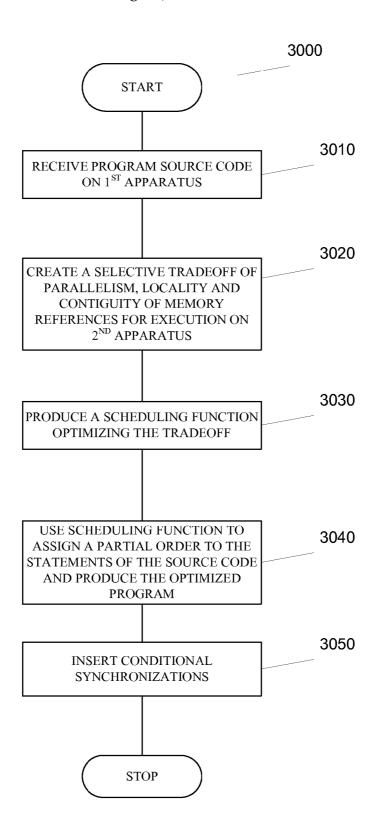

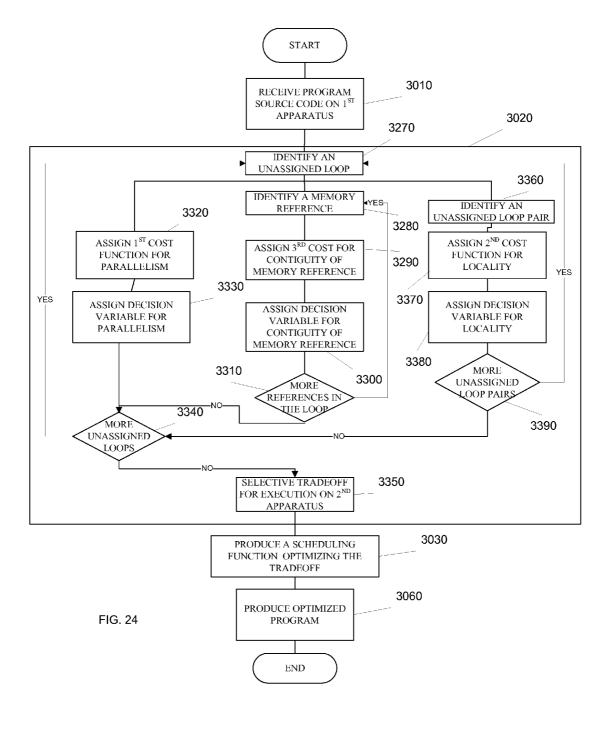

[0039] FIG. 23 illustrates embodiments of provided methods;

[0040] FIG. 24 illustrates other embodiments of provided methods:

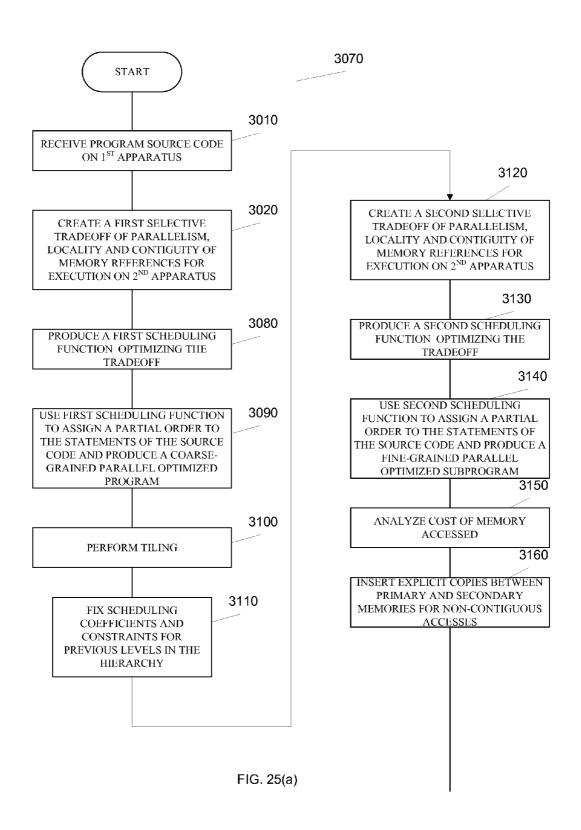

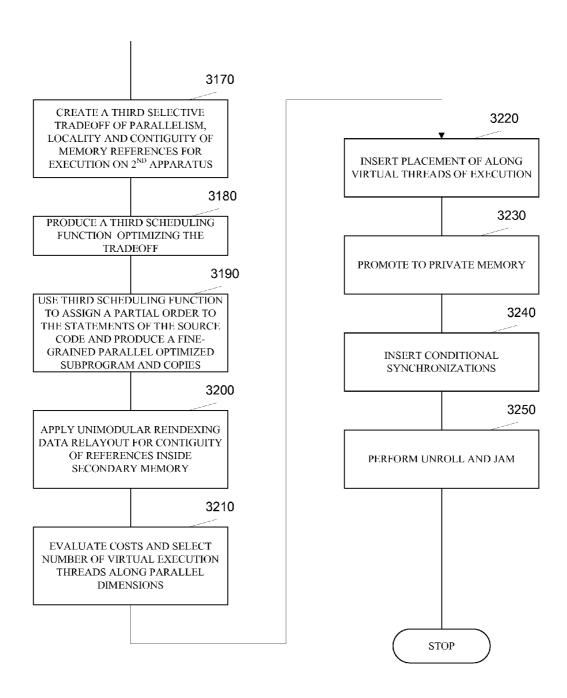

[0041] FIGS. 25a and 25b illustrate other embodiments of provided methods; and

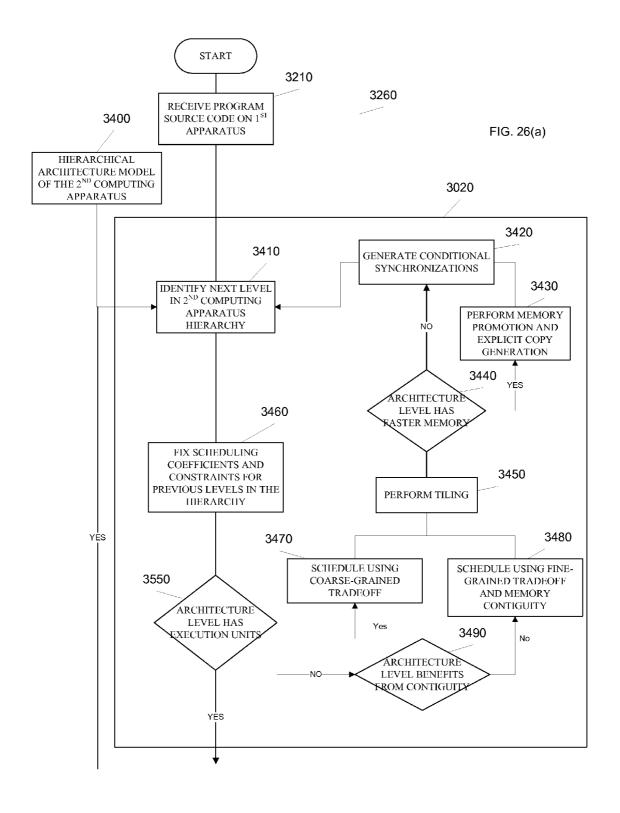

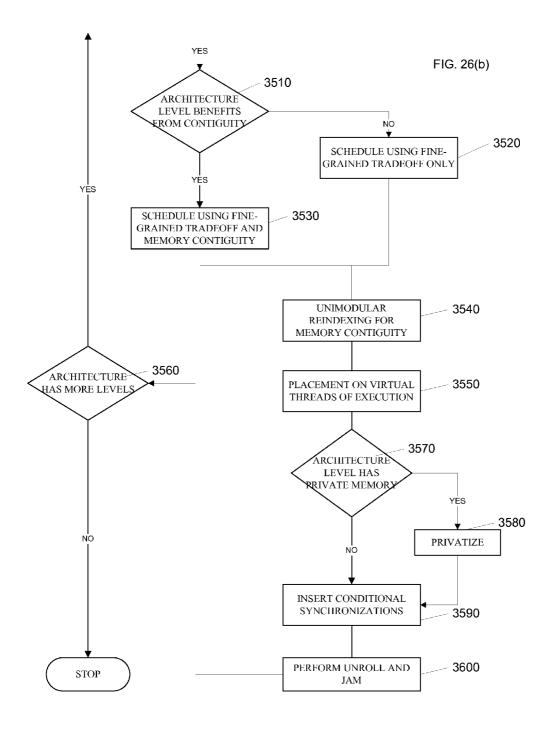

[0042] FIGS. 26a and 26b illustrate other embodiments of provided methods.

[0043] It will be recognized that some or all of the figures are schematic representations for purposes of illustration and do not necessarily depict the actual relative sizes or locations of the elements shown. The Figures are provided for the purpose of illustrating one or more embodiments with the explicit understanding that they will not be used to limit the scope or the meaning of the claims.

## DETAILED DESCRIPTION OF THE INVENTION

[0044] In the following paragraphs, the present invention will be described in detail by way of example with reference to the attached drawings. While this invention is capable of embodiment in many different forms, there is shown in the drawings and will herein be described in detail specific embodiments, with the understanding that the present disclosure is to be considered as an example of the principles of the invention and not intended to limit the invention to the specific embodiments shown and described. That is, throughout this description, the embodiments and examples shown should be considered as exemplars, rather than as limitations on the present invention. Descriptions of well known components, methods and/or processing techniques are omitted so as to not unnecessarily obscure the invention. As used herein, the "present invention" refers to any one of the embodiments of the invention described herein, and any equivalents. Furthermore, reference to various feature(s) of the "present invention" throughout this document does not mean that all claimed embodiments or methods must include the referenced feature(s).

[0045] The trend of increasing the frequency at which processors perform computations seems to have come to an end. Power consumption and control complexity have reached such high levels that manufacturers are backing out of this design path. Current machines have evolved to multiprocessor architectures on a chip with increasingly many cores per chip and multiple threads per core. This trend is expected to dramatically increase, reaching thousands of cores per chip in the next few years. Thus, modern computers increasingly need to exploit parallelism at different levels to provide sustained performance. On the other hand, parallel programming techniques have not evolved at the same speed and the gap between theoretical machine speed and actual utilization continues to increase.

[0046] Compilers are responsible for translating the abstract operational semantics of the source program, i.e., a text description of what the program's execution is supposed to perform, into an executable form that makes efficient use of a highly complex heterogeneous machine. Multiple architectural phenomena occur and interact simultaneously within the targeted computer during the execution of the program; this requires the optimizing compiler to combine multiple program transformations in order to define a program execution that takes advantage of those architectural phenomena. For instance, when targeting computers that have multiple processing elements (multi-core computers), there is often a trade-off between exploiting more processing elements simultaneously (parallelism) and exploiting data access locality to reduce memory traffic. Indeed, the speed and bandwidth of the memory subsystems are almost always a bottleneck. The problem is typically worse for multi-core computers. Since, in traditional compilers, optimization problems are associated with huge and unstructured search spaces, this combinational task is poorly achieved in general, resulting in poor scalability and disappointing sustained performance of the supposedly optimized program.

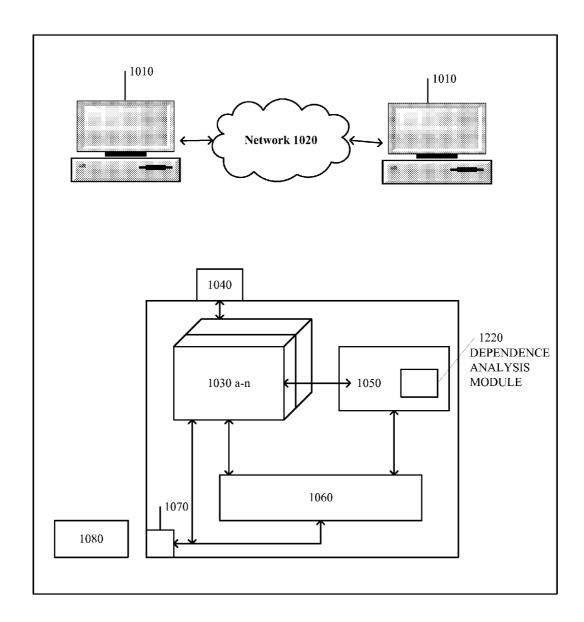

[0047] Generating efficient code for deep parallelism and deep memory hierarchies with complex and dynamic hardware components is a difficult task: the compiler (and runtime system) has to take the burden of tasks that only expert programmers would be able to carry. In order to exploit parallelism the first necessary step is to compute a representation which models the producer/consumer relationships of a program as closely as possible. The power of an automatic optimizer or parallelizer greatly depends on its capacity to decide whether two portions of the program execution may be interchanged or run in parallel. Such knowledge is related to the task of dependence analysis which aims at precisely disambiguating memory references. The issue is to statically form a compact description of the dynamic properties of a program. Forming a precise description is generally undecidable and approximations have to be made.

[0048] Once dependence analysis has been computed, a compiler performs program transformations to the code with respect to different, sometimes conflicting, performance criteria. Any program transformation must ultimately respect the dependence relations in order to guarantee the correct execution of the program. A class of transformations targeting the loop nests of a program (such as "DO" loops in the FORTRAN language, and "for" and "while" loops in languages derived from the Clanguage) are known to account for

the most compute intensive parts of many programs. The polyhedral model is a representation of a program's structure particularly suited for expressing complex sequences of loop nests, complex sequences of loop nest transformations, and other relevant information such as for instance dependences, communications, and array layouts.

[0049] A polyhedron is defined as a set of points verifying a set of affine inequalities and equalities on a number of variables. There exist alternate but equivalent definitions for polyhedrons, such as the one based on a combination of vertices, rays and lines proposed by Minkowski. There are also alternate representations, often based on the alternate definitions. While the present disclosure teaches using one of those definitions and representations to illustrate the various embodiments, various embodiments are in no way restricted to a particular definition or representation.

[0050] A polyhedral domain is defined as a finite union of polyhedrons. One of the main interests in using polyhedral domains is that they provide a precise representation of sets and relations among sets, on which many optimization problems can be phrased and solved using a rich set of algorithms, which are mostly available in the literature. Some embodiments of the sets in question represent loop iterations, monoand multi-dimensional data sets, sets of processing elements, data transfers, synchronizations, and dependences. Thus, essential characteristics of the execution of a program can be summarized into compact mathematical objects, polyhedrons, which can be manipulated and transcribed into an executable program that has desired execution properties.

[0051] By considering a subset of the variables of a polyhedron as symbolic constants, also called "parameters", it is possible to perform program optimizations and parallelization as a function of the symbolic constants. Hence, programs involving loops that depend on a constant value that is not known at the time when compilation is performed, but only when the program is executed, can be modeled using polyhedrons that are defined as a function of those constant values. A polyhedron involving parameters is called a parametric polyhedron. Similarly, a parametric polyhedral domain is defined by a finite union of parametric polyhedrons. For instance, the set of values that the counters of a loop nest reach during the execution of the loop nest is represented by the loop nest's "iteration domain". The iteration domain of the following loop nest (using the C language's syntax, where F is a C function call) can be written as the parametric domain

```

\begin{array}{l} P(n): \left\{ (i,j) \in Z^2 \mid 5 \leq i \leq n; 0 \leq j \leq 10; j \leq i \right\}: \\ for \ (i=5; \, i <=n; \, i++) \left\{ \\ for \ (j=0; \, j <=i \, \&\& \, j <=10; \, j++) \left\{ \\ F(i,j); \\ \right\} \end{array}

```

The set of iterations of such a loop nest depends directly upon the value of the parameters. The parametric domain that represents the set of iterations is called a "parametric iteration domain". It has to be noted that the values of the loop counters are integer. Hence, the set of values of i and j also lie on a regular lattice of integer points (the standard lattice  $Z^2$  in the current example). However, it is possible to represent the fact that a set belongs to a polyhedral domain as well as the fact that it also belongs to a regular lattice of points using polyhedral domains exclusively. While alternate, equivalent rep-

resentations exist (for instance those based on "Z-polyhedrons", which are an explicit intersection of a polyhedral domain and a lattice of integer points), various embodiments of the present invention are in no way restricted to exclusively using polyhedral domains. The use parametric polyhedral domains as a means to illustrate various provided embodiments. In some embodiments, either or both polyhedrons and Z-polyhedrons can be used as a representation, and there exist conversion methods between both representations.

**[0052]** While most of the transformations applied to the polyhedral representation of a program are defined for any element of the polyhedral domain to transform, a class of more complex and precise transformations is obtained by partitioning the vector space in which the polyhedral domain is defined into sub-polyhedrons, and by defining a different transformation for each polyhedron of the partition. The resulting transformation is called a "piecewise" transformation. For example, consider the transformation that takes two numbers i and j and computes three numbers x, y, and z as:  $\{x=2i+1; y=(i+j)/2; z=-3j+4\}$  when i is greater than and  $\{x=i; y=i-j+3; z=2j\}$  when i is less than or equal to j. It is a piecewise affine function since it has different definitions for each set of values,  $\{i>j\}$  and  $\{i\leq j\}$ , which define a partition of the (i,j) vector space.

[0053] The context of various embodiments, the use of polyhedral representations to perform complex optimizations on programs, either independently or within a system of optimizing components. An exemplary embodiment of such a system is illustrated in FIG. 1, where it is described as being part of a compiler. Flow of the exemplary embodiment starts in block 1, where the compiler is processing a program. Flow continues in block 14, where the compiler analyzes the program to decide if there are portions of the program that should be optimized and mapped using a polyhedral system. If it is the case, the flow goes to block 2, where the compiler provides the system of optimizing components with a polyhedral representation of a portion of the program to be optimized. If not, the compiler continues to process the program without using the system of optimizing components and completes. The components of the system are in charge of a part of the global optimization of the input program. In the flow of the embodiment illustrated in FIG. 1, the polyhedral representation of the input code is analyzed in block 2 to produce dependence information. Flow continues in block 3 where such information is used in a local memory compaction component or module that modifies array layouts in a way that removes some dependencies, schedules loop iterations in a way that exposes loops that scan independent iterations, and schedules the execution of operations using a same data to be executed within a close time interval. Flow continues in block 4, where the modified polyhedral representation of the program is processed by another optimizing component, which partitions the represented loop operations into entities called tasks, which have good data locality properties (they access a data set that involves an optimized use of the memory subsystem of the target computer), and assigns a processing element of the target machine to each task. In this exemplary embodiment, the flow continues to decision block 5, which decides which block is next in the flow as a function of the target machine. If the target machine requires the execution of explicit communication commands to transfer data to and from its processing elements, flow goes to block 6, where the representation of the program thus modified is then processed by a series of optimizing modules which define a new layout

for data that is transferred to a processing element's local memory. Otherwise, the flow goes to block 9. From block 6, flow continues to block 7, where a representation of the explicit communications is produced, based on polyhedrons, and then to block 8, where the execution of the communications are scheduled for parallel execution with the tasks, using multi-buffering. Whether the target machine requires explicit communications or not, the flow continues to block 9, where an optimizing component processes the polyhedral representation of the program obtained from the previous components by inserting a polyhedral representation of synchronization operations, which ensure that the execution of the modified program produces the same results or similar results as the original input program. The flow of the exemplary embodiment then goes to block 11, where an optimizing component partitions the tasks into subtasks whose execution reduces traffic between the processing elements' memories and their registers. Then, in block 12, a polyhedral representation of commands that trigger the execution of a series of tasks on the different processing elements of the target machine and that wait for the completion of those, is generated by the next optimizing component. Finally, in block 13, the polyhedral representation of the optimized program is transformed by polyhedral code generation component into a representation (Abstract Syntax Tree, high-level language code, or a compiler's internal representation) that can be either processed by a compiler or processed further by the user. In the exemplary embodiment, the flow continues back to block 1, where it may cycle again through the whole flow if there is more code to be optimized using the system of optimizing components

[0054] In contrast to compilers based on polyhedral domains, traditional loop-oriented optimizing compilers typically perform syntactic transformations. As a result, many interesting optimizations are often not available, such as fusion of loops with different bounds or imperfectly nested loop tiling.

[0055] In some embodiments, the optimizing components or modules comprise processor executable code that when executed by a processor, convert source code into other forms of source code, or in some instances machine code. In other embodiments, various modules may be implemented in hardware such as monolithic circuits, Application Specific Integrated Circuits (ASIC), or Field Programmable Gate Arrays (FPGA). These modules may comprise software, hardware, firmware, or a combination of these implementations. It is important to note that various embodiments are illustrated in specific programming languages, these illustrations are mere examples and the scope is not therefore limited to any particular programming language.

[0056] Embodiments of a provided optimization module, described above as local memory compaction are illustrated in FIGS. 2-8. FIG. 2 illustrates the flow of a provided method for local memory compaction. Flow begins in block 10 where source code is received into memory. In this embodiment, the source code represents loops with arbitrary parametric affine iteration domain and contains at least one array reference. An array reference is an operation that represents an access, typically a read or a write, to an array. Such a reference represents, either explicitly or implicitly, for instance by using programming language conventions, a function to retrieve the memory address of an element of the array. In loop programs, that function is typically a direct or indirect function of the loop indices and of some loop-constant values. For instance, in C, arrays are typically referenced through

mono- and multi-dimensional affine functions of some input values. In the C language, the declaration of an array includes parameters called "array size", which implicitly define the address of an array element as a function of the input values to references to this array declaring "char A[100][200]" allocates an array of 20000 elements (100×200), named A, and defines that for any two integer values x and y, the memory address of the element of A referenced through A[x][y] is b+200x+y, where b is a value called the "base address" of array A. b is constant for each array and is determined at some point in the compilation process. Flow continues to block 20 where inefficiencies in memory usage in the at least one array are identified. In one embodiment, the inefficiencies are related to access and memory footprint of the array. Flow then continues to block 30 where at least one local array is allocated, and in block 40 a portion of the array with inefficient memory usage is mapped into the local array. The mapping portion of the module outputs code that is more efficient than the original code in terms of the memory size requirements of the local array versus the original array. In some embodiments the accessed data is arbitrarily complex. In further embodiments, the mapping produces a piecewise affine index function for the local arrays. Other embodiments include the rendering of a visualization of the optimized code on a moni-

[0057] Arrays are typically allocated sets of contiguous memory blocks. Some loop operations may access only portions of the allocated memory. When reorganizing the data layout for a specific processor, there is an opportunity to take advantage of the inefficiencies in memory access requirements versus the actual utilization of the array. For example, given the following code fragment, 900,000 contiguous memory blocks are allocated, but only 100 are accessed in this operation. Furthermore, access to the array is not contiguous, but contains gaps, and thus will have less than optimal locality. Thus keeping the original data layout (and array size) in a remote processor is extremely inefficient. Moreover, if there are less than 900,000 blocks available in the local memory, the local memory cannot hold the entirety of the array and the program cannot be executed properly. In the provided code fragments, we are using "..." to elude other operations which do not have any specific illustrative purpose.

```

double A[300][300];

for (i=0; i<100; i++) {

...=...A[2*i+100][3*1]; }

```

[0058] One embodiment of a provided method, illustrated in FIG. 2, would map this code fragment into a local array with 100 elements. An exemplary mapping would produce the following pseudo-code fragment, in which the storage requirement of a local array is reduced from 300×300 elements to the optimal 100 elements.

```

double A_local[100]; //local memory transfer A[2*i+100][3*1] to A_local[i], i=0, 1, . . . 99; for (i=0; i<100; i++) { . . . = . . . A_local[i]; }

```

[0059] One feature of this embodiment is that it provides a method of compacting local memory in a computing appara-

tus. This method provides a more efficient memory structure in terms of both access to the elements and the amount of memory occupied by the data that is actually accessed. The memory requirements are reduced from the initial allocation to an allocation that is large enough to contain the data that is actually used in the operations. In contrast to other methods, the provided method handles loops whose iteration domains are non-rectangular, and loops that have a parametric iteration domain. In this document we refer to polyhedral iteration domains that are either non-rectangular or parametric or both as "arbitrary parametric iteration domains". In addition, the provided methods handle non-convex accessed data sets. The provided embodiments are very useful in image and video processing. Imaging applications typically utilize significant multi-dimensional arrays where data representations of physical objects and systems are stored. Many image processing steps, such as discrete wavelet transforms for example, only utilize discrete portions of the stored data. In these situations, various embodiments provide significant optimizations to local data storage.

[0060] Another embodiment of a provided method is illustrated in FIG. 3. In this embodiment, flow begins in block 10 where source code is received in memory. Similar to the above embodiment, the source code contains loops with arbitrary parametric iteration domain and contains at least one array reference. Flow continues to block 20 where inefficiencies in memory usage in the at least one array are identified. Flow then continues to block 30 where at least one local array is allocated, and in block 40 a portion of the array with inefficient memory usage is mapped into the local array. In this embodiment, mapping block 40 includes partitioning references to form compatible references in block 50; determining a relation within compatible references in block 60; grouping compatible references based on the relation in block 70; performing algebraic simplification in block 80; and performing geometric arrangement through re-indexing the elements of the local array in block 90. In some embodiments the set of references partitioned are references that access a portion of the array. The following pseudo-code example illustrates this embodiment.

```

\begin{array}{l} \mbox{float}\,A[256]\,[256]\,; \\ \mbox{doa}11\,\,(1=128^*j+16^*P;\,1 \le \min(-i+254,128^*j+16^*P+15);\,1++) \\ \mbox{doa}11\,\,(m=16^*k;\,m \le \min(-i+254,16^*k+15);\,m++) \\ \mbox{}\,A[1+i+m]\,\,[1+i+1]\,-=A[1-i+m]\,\,[i]\,\,^*\,A[i]\,\,[1+i+1]; \end{array}

```

[0061] In this case, all three references to array A are disjoint in that they access disjoint portions of the array. In this case, they are transformed into three local arrays A\_2, A\_3 and A\_4 in the following manner.

```

\begin{array}{l} \mbox{float A$\_2[16] [16]; // a triangular subregion of A} \\ \mbox{float A$\_3[16]; // a column of A} \\ \mbox{float A3 [16]; // a row of A} \\ \mbox{doa11 } (1=0;1 \le \min(15,-i-128*j-16*P+254);1++) \\ \mbox{doa11 } (m=0;m \le \min(i-i-6*k+254,15);m++) \\ \mbox{A$\_2[m] [1]$-=A$\_3[m]$*A$\_4[1];} \end{array}

```

[0062] Performing transformations of the way data are allocated in memory, i.e., transforming the data layouts, has a combinational aspect, since the data sets accessed through each array reference may overlap with one or more data sets

accessed by other array references. Since each one of those overlaps entail constraints in the way that data layouts can be transformed, analyzing all the combinations of overlaps for all the references is a source of high computational complexity. Hence, references are grouped into sets in such a way that data accessed through one set of references does not overlap data accessed through another set of references. In this embodiment, references of the same set are called "compatible references". Since there is no overlap among sets of compatible references, the following parts of the memory layout transformation, which consider the overlaps, can be applied independently to each set of compatible references. In particular, they will decide if the overlapping data sets accessed by a set of compatible references should be partitioned further and how.

[0063] In some embodiments, compatible references are identified by overlapping memory footprints during the execution of a particular subset of loop iterations. In an exemplary embodiment, the provided method identifies array references having overlapping memory footprints; duplicates a portion of the identified references; and associates each of the duplicates with disjoint subsets of the memory footprint. An example pseudo-code illustrates this embodiment.

```

double A[100] [100];

for (j = 0; j \le 100; j++) {

\dots = A[i] [j] * A[j] [i];

}

```

[0064] The two references A[i] [j] and A[j] [i] overlap when i=j. However, if the references are allocated together, it is impossible to reduce the local memory usage using only affine transformations. This is because the data footprint of the two references is a 2-dimensional set (a cross), while the data footprints of the individual references are both 1-dimensional. In order to compute better allocations in situations like this, one embodiment first estimates how much overlapping is in the references. If the references are read-only, and if the overlapping data set is a small percentage of the overall data set, the embodiment splits the references into two distinct references to one-dimensional data sets. In the above example, the embodiment will generate the following local memory allocation. Note that the center element of the data foot print, A[i][i], has been replicated and put into the locations A\_1 [i] and A\_2 [i].

```

\label{eq:double_A_1[i00];} \begin{split} & \text{double A}\_1[i00]; \\ & \text{double A}\_2[i00]; \\ & \text{Transfer A[i] [j] to A}\_1[i], i = 0 \dots 99 \\ & \text{Transfer A[j] [i] to A}\_2[i], i = 0 \dots 99 \\ & \text{for (j 0; } j < 100; j++) \\ & \dots A}\_1[j] *A\_2[j]; \end{split}

```

[0065] The geometric re-arrangements provided by a further exemplary embodiment are defined by a piecewise affine transformation. In other words, the transformation applied to the references is defined as a set of functions, each element of the set being valid within a polyhedral domain of the loop values, the parameters and the coordinates of the data accessed through the set of compatible references. In an exemplary embodiment, when some of the data accessed by a set of compatible references are written by some of the ref-

erences, the written data subset and a subset of the data set that is only read define a partition for the piecewise affine transformation. Consider the program represented by the following pseudo-code:

```

double A[100][100];

for (j = 0; j < 99; j++) {

A[i] [j+1] = ... A[j] [i];

}

```

[0066] In this example, the data set accessed by the both references to array A form a two-dimensional set, while the data sets accessed through each reference are one-dimensional. The data accessed through both references overlap in A[i][i]. In the exemplary embodiment, a piecewise transformation of A is applied, which separates A into two subsets, one for each one-dimensional data set, and marks one of them as receiving the updates (let us call it the "writing reference") to the duplicated data. In the example, the duplicated data is A[i][i] and the iteration domain is partitioned into three polyhedral domains,  $\{0 \le j \le i\}$ ,  $\{j = i\}$  and  $\{i \le j \le 99\}$ , in order to take into account the fact that only one of the data subsets is updated. Such a partition of the iteration domain is obtained by defining the iterations accessing duplicate data through "non-writing" references and replacing those accesses with an access through the writing reference. The resulting piecewise affine transformation is  $\{(A[i][j-1]=A_1[j], A[j][i]=A_1[j], A[j][i]=A_$ 2[j]) for  $0 \le i < 100$ ,  $0 \le j < i$  or i < j < 100; and  $(A[i][j-1] = A_1[j]$ ,  $A[j][i]=A_1[j]$  for  $0 \le i < 100$ , i=j. The result of the piecewise affine transformation can be represented by the following pseudo-code, which uses only two arrays as a replacement for the original array A, has quasi-optimal memory requirements (198 memory cells, while the optimal would be 197):

```

\begin{array}{l} \text{double A\_1[99], A\_2[99]} \\ \text{for (int j=0; j<i; j++) } \{ \\ \text{A\_1[j]} = \dots \text{A\_2[j];} \\ \} \\ \text{A\_1[i]} = \dots \text{A\_1[i-1]; // the updated value of} \\ \text{A[j][i] is in A\_1[j] when j=i for (int j=i+1; j<99; j++) } \{ \\ \text{A\_1[j]} = \dots \text{A\_2[j];} \\ \} \end{array}

```

[0067] In other exemplary embodiments, the geometric rearrangement is a piecewise affine transformation that defines a partition of the iteration domain and of the data sets in such a way that the number of references to a local array varies from one element of the partition to another. In the following example, in which the possible values of variable i are  $\{0 \le i \le 99900\}$ , the data sets accessed through reference A[j] and A[i+j] overlap when i is less than 100. Otherwise, they do not overlap.

```

double A[10000];

for (j =0; j< 100; j++) {

A[i] = . . . * A[i+j]

}

```

[0068] Since those data sets overlap for some values of i, both references are put in the same group of compatible references. If the accessed data sets are allocated as a single

local array, the amount of memory necessary to contain the array is 10000 memory cells. On the other hand, if they are allocated as two separate arrays, some of the data would have to be duplicated and the iteration domain (the j loop here) would have to be partitioned as in the previous exemplary embodiment. The amount of overlap when i is less than 100 may not be small enough and it may not be profitable to perform the duplication. The geometric rearrangement provided by the embodiment is a piecewise affine transformation that defines a partition of the set of parameters (in the current example, i):  $\{(A_1[i]=A[i]) \text{ for } 0 \le i < 100, \text{ and } (A_1[i]=A[i]),$  $A_2[j]=A[i+j]$  for  $i \le 100$ ). The maximum amount of memory that has to be allocated for any value of i is 200 memory cells (as compared to 10000), and it is 100+i when i is less than 100. The resulting transformation can be represented as pseudo-code as follows:

```

\begin{array}{l} \text{if (i < 100) } \{ \\ \text{double A}\_1[100+i]; \\ \text{for (j = 0; j < 100; j++) } \{ \\ \text{A}\_1[j] = ...* \text{A}\_1[i+j] \\ \} \\ \text{else } \{ \\ \text{double A}\_1[100]; \\ \text{double A}\_2[100]; \\ \text{for (j = 0; j < 100; j++) } \{ \\ \text{A}\_1[j] = ...* \text{A}\_2[j]; \\ \} \\ \end{array}

```

[0069] One advantage of the geometric rearrangement that is performed by this exemplary embodiment is that the j loops are not partitioned. Partitioning the loops into smaller loops is often a factor of performance degradation, which is avoided in this exemplary embodiment. The partition of i is obtained by computing the domain in which both data sets intersect, by projecting the intersection onto the vector space of the parameters (in the current example, the parameter is i and the projected domain is  $\{i<100\}$ .

[0070] The operation flow of a further provided embodiment of a local memory compaction module is illustrated in FIG. 4. In this embodiment, flow begins at block 10 where source code is received in memory. Similar to the above embodiment, the source code represents loops with arbitrary parametric affine iteration domains and contain at least one array reference. Flow continues to block 20 where inefficiencies in memory usage in the at least one array are identified. In this embodiment, the identification of inefficiencies includes block 100 where strides in the polyhedral domain that defines the accessed dataset are identified, and block 110 where a lattice of integer points within the domain is extracted from the domain. These integer points indicate that only a regular subset of the accessed data region is accessed. In this manner, more efficient allocation of local arrays is accomplished because portions of the array that are not accessed are identified and excluded from the mapping from the array to the local array.

[0071] An additional provided embodiment is illustrated in FIG. 5. In this embodiment, like earlier embodiments flow begins at block 10 where source code is received in memory. Similar to the above embodiment, the source code represents loops with arbitrary parametric affine iteration domain and contains at least one array reference. Flow continues to block 20 where inefficiencies in memory usage in the at least one

array are identified. Flow then continues to block 30 where at least one local array is allocated, and in block 40 a portion of the array with inefficient memory usage is mapped into the local array. In this embodiment, like in the embodiment illustrated by FIG. 3, mapping block 40 includes partitioning references to form compatible references in block 50; determining a relation within compatible references in block 60; grouping compatible references based on the relation in block 70; performing algebraic simplification in block 80; and performing geometric arrangement in block 90. The algebraic simplification block 80 includes block 130 where a representative array reference is extracted from a set of references accessing a portion of the array. In some embodiments, the representative array reference represents a set of references which access polyhedral datasets whose accessed points all lie on a lattice of integer points that is not the standard lattice, on which any integer point lies. These embodiments take advantage of the fact that array references represent affine functions, which can be represented as matrices called "access matrices". In the exemplary embodiment, the flow within block 40 goes from block 130 to block 140 where a Hermite factorization is performed for the access matrix representing the representative array reference. The Hermite factorization produces a piecewise affine index function.

**[0072]** One purpose of Hermite factorization is to reduce the dimension of the reference to the actual geometric dimension of the data footprint. In addition, if the access pattern contains strides, i.e., regular intervals between accessed data, using the non-unimodular matrix that results from the Hermite factorization in the transformation removes these strides in the resulting local references. For example, given an affine access function f(x, y) on loop indices x and parameters y, we first decompose it into the sum of g(x)+h(y), where g(x) is a linear function on x and h(y) is an affine function on y. This decomposition is an algebraic simplification that makes it possible to perform further computations on the part of f(x,y) that involves variables only. Function g(x) can be decomposed into g(x)=HU, where H=[H'0] is the Hermite Normal Form of g(x) and U is unimodular matrix. Let

$$U = \begin{bmatrix} U_1 \\ U_2 \end{bmatrix}$$

where HU=H'U1•The following mapping from global to local indices is then performed  $f(x, y) f \rightarrow U1x$ .

[0073] Hermite factorizations have many uses is lattice computations. The Hermite factorization of a matrix G, written G=HU, writes matrix G as the product of two matrices, H and U. H, called the "Hermite normal form", is a canonical representation of the lattice (also) represented by G. U is a unimodular matrix, which entails that U, when used as a transformation, always transforms any point that has integer coordinates into another point that has integer coordinates. Also, any point that has integer coordinates can be obtained by transforming a point with integer coordinates using a unimodular transformation. This is important since most programming language conventions enforce that data elements, and particularly array elements, must have integer coordinates.

[0074] The flow of a still further provided embodiment is illustrated in FIG. 6. In this embodiment, like previous embodiments, flow begins at block 10 where source code is

received in memory. Similar to the above embodiment, the source code represents loops with arbitrary parametric affine iteration domain and contain at least one array reference. Flow continues to block 20 where inefficiencies in memory usage in the at least one array are identified. Flow then continues to block 30 where at least one local array is allocated, and in block 40 a portion of the array with inefficient memory usage is mapped into the local array. In this embodiment, mapping block 40 includes partitioning references to form compatible references in block 50; determining a relation within compatible references in block 60; grouping compatible references based on the relation in block 70; performing algebraic simplification in block 80; and performing geometric arrangement in block 90. Geometric rearrangement 90 contains blocks 150 where linear constraints are formed, block 160 where sets of linear programming problems are formed from the linear constraints and solved, and block 170 where a data reindexing is computed. In some embodiments, the flow goes back to block 150. In such embodiments, geometric rearrangements are applied iteratively until no reindexing function is found that reduces memory requirements. [0075] Most modern programming languages abide by the convention that multi-dimensional arrays are allocated in memory as if they were canonical rectangular parallelotopes. In a space of d dimensions, a parallelotope is a finite polyhedron defined by 2d faces, and whose faces are pair-wise parallel. A canonical rectangular parallelotope is a parallelotope for which the normal vectors to its faces are either a canonical vector or the negation of a canonical vector. Examples of rectangular parallelotopes are a cube (in a 3-dimensional space) and a rectangle (in a 2-dimensional space). In an exemplary embodiment, the transformation is a unimodular reindexing of the accessed data that minimizes the size of the smallest canonical rectangular parallelotope that encloses the accessed dataset. The smaller the enclosing rectangular parallelotope, the smaller the amount of memory that has to be allocated for the dataset.

[0076] In some embodiments, this is accomplished by formulating a first set of linear constraints through the use of Farkas Lemma. This first set of linear programming constraints is decomposed dimension by dimension to form a set of integer linear programming problems. This set of problems is then solved to provide the data reindexing function which can then be applied to the at least one local array. Unimodular reindexings transform integer points into integer points. Hence, the convention that data elements have integer coordinates is preserved by such a reindexing. In the case of affine transformations, the linear part of the transformation can be represented by a unimodular matrix.

[0077] Farkas lemma is a basic linear algebra theorem which is often used to obtain, from a set of affine constraints (i.e., inequalities and equalities) on variables with unknown coefficients, constraints that apply to the unknown coefficient themselves. In this embodiment, it is used to obtain a set of constraints involving the coefficients of the unimodular data reindexing function (which is represented as a matrix) and the width of the enclosing rectangular parallelotope along each dimension. From those obtained constraints, the method embodiment finds values of the coefficients of the unimodular data reindexing function for which the width is minimal, using integer linear programming. For example, the data set accessed through reference B[i+j][j] in the following pseudocode can be reindexed so as to occupy only 100 memory cells:

```

Double A[n+10][n+10];

Double B[[2n+20][n+10];

For (i=n; i<n+10; i++) {

For (j=n; j<n+10; j++) {

A[i]j] = ... B[i+j][i];

}

```

**[0078]** The coordinates  $(x_1, x_2)$  of the elements of array B accessed by that loop node are defined by the constraints D: $\{n \le x_2 < n+10; n \le x_1 < n+10\}$ . The embodiment finds values of the coefficient of a matrix U such that U is unimodular and the coordinates  $x'_1$  and  $x'_2$  of the reindexed data are defined by:

$$\begin{bmatrix} x_1' \\ x_2' \end{bmatrix} = U \begin{bmatrix} x_1 \\ x_2 \end{bmatrix} + \begin{bmatrix} t_1 \\ t_2 \end{bmatrix} n + \begin{bmatrix} t_{01} \\ t_{02} \end{bmatrix}$$

The set of possible values of the coefficients of U, as well as the possible values of t1, t2,  $t_{01}$  and  $t_{02}$  are defined from the set of constraints D and the constraints that the data  $(x^1, x^1_2)$  are enclosed in a rectangular parallelotope of size  $(s_1, s_2)$  using Farkas lemma. Then, a value for those coefficients is computed for which the size of the smallest enclosing rectangular parallelotope  $(s_1, s_2)$  in our example) is minimal. Those values are computed by solving, dimension by dimension of the data set, an integer linear programming problem.

[0079] An integer linear programming problem defines a linear function of a set of variables, called the "objective function" and whose minimal (or, alternatively, maximal) value over a polyhedral domain called the "feasible set", is looked for. Solvers for such problems typically return a polyhedral domain, within the feasible set, for which the value of the objective function is minimal. In the running example, the embodiment finds:

$$\begin{bmatrix} x_1' \\ x_2' \end{bmatrix} = \begin{bmatrix} 1 & -1 \\ 0 & 1 \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \end{bmatrix} + \begin{bmatrix} -1 \\ -1 \end{bmatrix} n + \begin{bmatrix} 0 \\ 0 \end{bmatrix}$$

The following pseudo-code represents the program resulting from the data reindexing of array B in our running example:

```

Double A[10][10];

Double B[[2n+20][n+10];

For (i=n; i<n+10; i++) {

For (j=n; j<n+10; j++) {

A[i]j] = ... B[j-n][i-n];

}

```

The data footprint of the re-indexed array B is now reduced to 100 memory cells, instead of  $n^2+20n+100$  initially.

[0080] In one of the exemplary embodiments, the unimodular nature of the reindexing matrix U is obtained by forcing U to be triangular and forcing the absolute value of the diagonal elements to be one. In another embodiment, the unimodular nature of the reindexing matrix is obtained by composition of an upper triangular unimodular and a lower

triangular unimodular matrix. The advantage of that other embodiment is that the class of unimodular reindexing functions produced is not limited to the reindexing functions represented by a triangular matrix. Finding those two matrices is equivalent to reindexing data twice, first by finding an upper triangular reindexing matrix as described above and applying the reindexing, and then by finding a lower triangular reindexing matrix for the reindexed set and by applying that second reindexing. Yet another embodiment produces, in the same way, a unimodular reindexing by composition of an upper triangular unimodular matrix, a permutation matrix and a lower triangular unimodular matrix. The advantage of the embodiment is that the class of reindexing function that can be produced is the whole class of integer unimodular matrices.

[0081] Turning to FIG. 7 which illustrates another embodiment of a provided method, like the previous embodiments. flow begins in block 10 where source code is received in memory. Similar to the above embodiment, the source code represents loops with arbitrary parametric affine iteration domain and contains at least one array reference. Flow continues to block 20 where inefficiencies in memory usage in the at least one array are identified. Flow then continues to block 30 where at least one local array is allocated, and in block 40 a portion of the array with inefficient memory usage is mapped into the local array. In this illustration, block 40 contains block 180 where a parallelotope of minimal volume is derived this parallelotope enclosing the domain of the data set accessed by the local arrays. Block 40 additionally contains block 190 where a finite prism of triangular base is derived.

[0082] As used herein, a finite prism is a polyhedron defined by a set of translations of a "base" polyhedron, which lies in a subspace of the considered space, by a finite convex set of linear combinations of vectors of the complementary subspace. Since they are finite, it is possible to characterize the maximum extent of a finite prism along the directions of the complementary subspace. In this document, those extents are called "height" of the prism (there is one height along every direction of the complementary subspace). A triangular prism is a prism whose base polyhedron is a triangle. In two dimensions, it is just a triangle. In one embodiment, this finite prism has a minimum volume that encloses the data footprint domain. In block 200 the prism is compared to the parallelotope. In block 210 the prism is partitioned into two prisms. One of the two is then transformed using a central symmetry such that the union of the transformed prism and the nontransformed prism has a smaller memory footprint than the enclosing parallelotope. One advantage of that embodiment is that it provides data layouts that have smaller memory requirements, for a class of accessed datasets for which methods based on parallelotopes are not optimal.

[0083] For instance, the dataset accessed by the program represented by the following pseudo-code through reference B is triangular:

```

For (i=0; i< 10; i++) {

For (j=0; j< i; j++) {

... = ... B[i][j];

}

```

[0084] The embodiment finds three constraints that enclose the accessed data set, in a similar way as in the embodiment depicted in FIG. 6, using the Farkas lemma. The minimal volume for a parallelotope that encloses the dataset would be about twice the volume of the triangle. Hence, using such a parallelotope to determine the memory allocation of the dataset is bound to be sub-optimal. Instead, the current embodiment, depicted in FIG. 7, defines a tighter enclosing polyhedron using three inequalities (it is then a prism of triangular base). Using the enclosing prism, the data set is partitioned in two subsets, say A and B, and subset A is re-indexed in such a way that both the array elements in B and the re-indexed elements are enclosed in a smaller parallelotope than the original parallelotope. The volume of the new parallelotope is about the volume of the prism of triangular base. Since there is a parallelotope of smaller volume enclosing the reindexed data set, its memory requirements are smaller. The result is a piecewise affine array reindexing, which typically partitions the loop iterations into the iterations that access A, and the ones that access B.

**[0085]** In the current embodiment, the three inequalities  $\{(a): aI+a_0\ge 0; (b):bI+b_0\ge 0; (c): cI+c0\ge 0\}$  that define the triangular prism P, where I is the vector of data coordinates are used to devise the partitioning. Let  $x_w$  a point in the intersection of (b) and (c) and let  $w=ax_wI+a_0$ . The prism is partitioned into A and B as follows:

$$A = P \cap \left\{ aI + a0 - \frac{w+1}{2} \ge 0 \right\}$$

and B=P-A. A point,  $x_0$ , is defined that is in the domain  $\{aI+a_0-w+1<0; bI+b_0<0\}$  whose coordinates are a multiple of 1/2 and whose "height" in the prism is about half of the height of the prism. Array elements that are defined by A are transformed using a central symmetry of center  $x_0$ . In the program represented by the following pseudo-code, the tightest enclosing parallelotope, defined by  $\{0 \le x1 \le 9\}$ , where x1 represents the first dimension of array C and x2 its second dimension, includes 100 array elements.

```

Double C[10][10];

For (i=0; i< 10; i++) {

For j=0; j< i; j++) {

... C[i,j] ...;

}

}

```

[0086] The tightest enclosing triangle, defined by  $\{0 \le x1; 0 \le x2; x1+x2 \le 9\}$ , by comparison, includes 55 elements, which is about half the number of elements required for the enclosing parallelotope. Since the number of array elements in the enclosing triangle is less than the number of array elements in the enclosing parallelotope, the embodiment considers the tightest enclosing triangle and partitions the enclosed data into data subsets A:  $\{0 \le x_1; 5 \le x_2; x_1+x_2 \le 9\}$  and B:  $\{0 \le x_1; 0 \le x_2 \le 4; x_1+x_2 \le 9\}$ . Point

$$x_0 = \left(5, \frac{9}{2}\right)$$

is selected as center of symmetry and the elements of A are then transformed into a new array subset A' as follows:

$$\left\{x_1' = (2^*5) - x_1; x_2' \left(2^* \frac{9}{2}\right) - x_2\right\},\,$$

where  $(x'_1,x'_2)$  are the new array element coordinates. The resulting program can be represented by the following code:

$$\begin{array}{c} \text{Double C[11][5];} \\ \text{For } (i=0; i<10; i++) \left\{ \\ \text{For } (j=0; j<=4 \&\& j$$

The accessed data set is included in the parallelotope  $\{0 \le x1 < 11, 0 \le x2 < 5\}$ , whose memory requirements are of 55 memory cells, i.e., about half of the parallelotope before the transformation. Other data layout optimizations, which are optimal when there is a tight parallelotope enclosing the accessed dataset, will then be more optimal than if applied straightforwardly to the original dataset that can be enclosed more tightly with a triangular prism.

[0087] FIG. 8 illustrates a further embodiment of a provided method. In this embodiment, flow begins in block 10 where source code is received in memory. Similar to the above embodiment, the source code contains loops with arbitrary parametric affine iteration domain and contain at least one array reference. Flow continues to block 20 where inefficiencies in memory usage in the at least one array are identified. Flow then continues to block 30 where at least one local array is allocated, and in block 40 a portion of the array with inefficient memory usage is mapped into the local array. Flow then continues to block 220 where asynchronous communications and wait operations are generated. The exemplary embodiment uses the mapping between local memory elements and the elements of the original arrays, in conjunction with a description of the data that are needed as input and produced as output of the tasks to be executed, to produce an abstract representation of the transfers between the original arrays and the local memory elements. In an exemplary embodiment, the generation of these communications and wait operations includes the use of multi-buffering for overlapping communication and computation operations.

[0088] Many computers that contain processors that have an explicitly managed local memory also have the ability to transfer data at the same time as they are performing other computations. Such transfers are called "asynchronous". The main reason for using that feature is that the typical time necessary for such transfers is often comparable to the time taken to perform computations between two consecutive transfers of input data. Since doing both transfer and computation at the same time takes less time than doing one after another, the effect of overlapping them is to improve the overall program execution time. The use of several memory zones, specialized to either execution, reception or sending of data, makes the overlap possible. Such a use is called "multi-buffering". The specialization of the buffers is also modified

at certain times. Such a modification is called a "rotation of the buffers", since a buffer is cyclically assigned the same specialization.

[0089] One embodiment computes a local memory mapping, adds a polyhedral representation of the communications and schedules communications and computations in a multibuffering scheme for the program represented by the following pseudo-code. In this pseudo-code, every iteration of the k loop works on a distinct instance of local memory:

```

\begin{array}{c} \text{for } (k=0;\, k <=7;\, k++) \; \{ \\ \text{for } (l=0;\, l <=15;\, l++) \; \{ \\ \text{for } (m=0;\, m <=15;\, m++) \; \{ \\ \text{for } (n=16 * k;\, n <=16 * k+15;\, n++) \; \{ \\ C[l][m] = C[l][m] + A[l][n] * B[n][m]; \\ \} \\ \} \\ \} \\ \} \\ \end{array}

```

[0090] This results in a program that can be represented by the following pseudo-code:

In the code example, "Get" operations are transfers from an original array to a re-indexed array in local memory. "Put" operations are transfers from local memory to original array. While the values of k in the original program were going from 0 to 7, in the multi-buffered version produced by the embodiment they are going from -1 to 8. At iteration k=-1, the first "get" transfers are issued. At iteration k=8, the last "put" transfers are issued. "Wait" operations, which wait for the completion of a series of transfers, were also inserted to ensure that a transferred data set is completed at that point of the program's execution. In the embodiment, a tag system is used to identify the transfers whose completion is to be waited upon. The "rotate" operations operate the buffer rotation.

[0091] Illustrated in FIG. 9 are computing apparatus and computer software products consistent with provided embodiments. Computing apparatus 720 includes processor 660, memory 670, storage medium 680, and in some embodiments input port 690 and network interface 710. In many provided embodiments, storage medium 680 contains a set of processor executable instructions that when executed by processor 660 configure computing apparatus 720 to implement the modules and methods described herein. In one embodi-

```

for (k = -1; k \le 8; k++)

if (k \le 7 \&\& k \ge 0)

wait(tag=0);

rotate(vars=[C_l, A_l, B_l]);

for (l = 0; l \le 15; l++) {

for (m = 0; m \le 15; m++)

get(src=\&B[1][16 + 16 * k + m], dst=\&B_1<1>[1][m], tag=0);

for (l = 0; l \le 15; l++)

for (m = 0; m \le 15; m++)

get(source=&A[l][m], destination=&A_l<1>[l][m], tag=0);

for (1 = 0; 1 \le 15; 1++)

for (m = 0; m \le 15; m++) {

get(src=&C[l][16 + 16 * k + m, tag=0);

if (k \ge 1) wait(tag=1);

if (k \le 7 \&\& k \ge 0)

for (l = 0; l \le 15; l++)

for (m = 16 * k; m \le 16 * k + 15; m++)

for (n = 0; n \le 15; n++)

C_{l[l][-16 * k + m]} = C_{l[l][-16 * k + m]} + B_{l[n][-16 * k + m]} *

A_l[l][n];

for (l = 0; l \le 15; l++)

for (m = 0; m \le 15; m++)

put(src=\&C_{[l][m]}, dst=\&C[l][16 * k + m], tag=1);

```

ment, storage medium 680, containing the set of processor executable instructions resides in another computing apparatus 720 across network 730. In an embodiment of a computer software product, computer software product 700 is a computer readable storage medium containing processor executable instructions sufficient that when executed by processor 660 configure computing apparatus 720 to implement the above described modules and methods. Further, computer software product, in some embodiments consists of a physical medium configured to interface with input port 690 to allow its contents to be copied to storage medium 680. In other embodiments, computer software product 700 is an internal storage medium, such as 680. An additional embodiment of computing apparatus 720 includes a plurality of processors **680**(a-n), a plurality of memories **670**(a-n), a storage medium 680 and in some embodiments input port 690 and network connection 710. In some embodiments, one or more processors 680(a-n) is a host, while others are modeled in the form of a grid.